在當(dāng)今數(shù)字化時代,軟件設(shè)計師扮演著將抽象概念轉(zhuǎn)化為實際應(yīng)用的關(guān)鍵角色。許多初入行的開發(fā)者常常將注意力集中在高級編程語言、框架和設(shè)計模式上,而忽視了支撐這一切的底層基礎(chǔ)——計算機(jī)組成原理與體系結(jié)構(gòu)。理解這些基礎(chǔ)并非硬件工程師的專屬,對于軟件設(shè)計師而言,它們同樣是提升設(shè)計能力、編寫高效代碼、解決復(fù)雜系統(tǒng)問題的核心知識。

計算機(jī)組成原理:理解軟件的物理載體

計算機(jī)組成原理揭示了計算機(jī)硬件系統(tǒng)的內(nèi)部工作機(jī)制。對于軟件設(shè)計師來說,這不僅僅是理論知識,更是理解程序如何被執(zhí)行的起點(diǎn)。

1. 處理器與指令集

中央處理器(CPU)是計算機(jī)的大腦,軟件設(shè)計師編寫的代碼最終都會轉(zhuǎn)化為CPU能夠理解的機(jī)器指令。了解指令集架構(gòu)(ISA),如x86、ARM或RISC-V,有助于理解不同平臺上的性能差異和兼容性問題。例如,知道CPU的流水線、分支預(yù)測和亂序執(zhí)行機(jī)制,可以幫助開發(fā)者編寫對緩存更友好的代碼,減少分支誤預(yù)測,從而提升程序運(yùn)行效率。

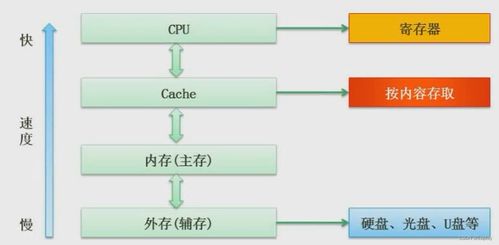

2. 存儲器層次結(jié)構(gòu)

從寄存器、高速緩存(Cache)、主存(RAM)到輔助存儲器(如SSD、HDD),存儲器的訪問速度和成本呈指數(shù)級差異。軟件設(shè)計師若不了解緩存行(Cache Line)、局部性原理(時間局部性與空間局部性),很可能寫出導(dǎo)致大量緩存未命中(Cache Miss)的代碼,即使算法時間復(fù)雜度相同,實際性能也可能相差數(shù)倍。在設(shè)計數(shù)據(jù)密集型應(yīng)用時,合理組織數(shù)據(jù)結(jié)構(gòu)以匹配緩存行為,往往是性能優(yōu)化的關(guān)鍵。

3. 輸入輸出系統(tǒng)

I/O操作通常是性能瓶頸所在。理解中斷、DMA(直接內(nèi)存訪問)以及各種總線協(xié)議,能讓軟件設(shè)計師更好地進(jìn)行異步編程、設(shè)計高并發(fā)系統(tǒng),并合理選擇阻塞與非阻塞I/O模型。例如,在網(wǎng)絡(luò)編程中,了解數(shù)據(jù)從網(wǎng)卡到應(yīng)用層的內(nèi)存拷貝過程,有助于選擇像零拷貝(Zero-copy)這樣的高效技術(shù)。

計算機(jī)體系結(jié)構(gòu):軟件與硬件的橋梁

計算機(jī)體系結(jié)構(gòu)關(guān)注的是計算機(jī)系統(tǒng)的概念性結(jié)構(gòu)和功能特性,它定義了軟件與硬件之間的接口。

1. 系統(tǒng)架構(gòu)的影響

無論是傳統(tǒng)的馮·諾依曼結(jié)構(gòu),還是現(xiàn)代的哈佛結(jié)構(gòu)(分離指令與數(shù)據(jù)存儲器),亦或是異構(gòu)計算(如CPU+GPU),不同的體系結(jié)構(gòu)直接影響軟件的設(shè)計范式。例如,在GPU上進(jìn)行通用計算(GPGPU)需要采用大規(guī)模并行編程模型(如CUDA、OpenCL),這與傳統(tǒng)的串行CPU編程思維截然不同。軟件設(shè)計師需要根據(jù)目標(biāo)平臺的體系結(jié)構(gòu)特點(diǎn),選擇合適的設(shè)計模式和算法。

2. 并行與多核體系

多核處理器已成為主流,但如何讓軟件充分利用多個核心是軟件設(shè)計師面臨的挑戰(zhàn)。理解對稱多處理(SMP)、內(nèi)存一致性模型(如順序一致性、弱一致性)、以及緩存一致性協(xié)議(如MESI),是設(shè)計正確、高效多線程程序的基礎(chǔ)。缺乏這些知識,很容易陷入競態(tài)條件、死鎖和可見性等問題,且難以發(fā)揮硬件并行能力。

3. 虛擬化與抽象層

從操作系統(tǒng)對硬件的抽象,到虛擬機(jī)監(jiān)控器(Hypervisor)對完整計算機(jī)環(huán)境的虛擬化,再到容器對操作系統(tǒng)資源的隔離,現(xiàn)代軟件開發(fā)建立在層層抽象之上。理解這些抽象背后的機(jī)制(如虛擬內(nèi)存、系統(tǒng)調(diào)用、上下文切換),能幫助軟件設(shè)計師更深刻地理解程序運(yùn)行環(huán)境,更好地進(jìn)行系統(tǒng)級調(diào)試和性能剖析。

軟件開發(fā)實踐中的具體應(yīng)用

1. 性能優(yōu)化

一個優(yōu)秀的軟件設(shè)計師不應(yīng)只滿足于功能實現(xiàn)。當(dāng)性能成為需求時,底層知識便不可或缺。例如:

- 算法選擇:在數(shù)據(jù)量極大時,即使O(n log n)的算法,也可能因為頻繁的緩存未命中而慢于理論上更差的O(n2)算法,如果后者具有更好的局部性。

- 內(nèi)存管理:理解內(nèi)存分配器的工作原理、內(nèi)存碎片問題,可以幫助在C/C++等語言中更有效地管理內(nèi)存,或在Java/.NET中理解垃圾收集器的行為并進(jìn)行調(diào)優(yōu)。

- 編譯與鏈接:了解編譯器優(yōu)化(如循環(huán)展開、內(nèi)聯(lián))、鏈接器對符號的解析過程,有助于理解編譯期錯誤、運(yùn)行時庫依賴,甚至進(jìn)行跨平臺構(gòu)建。

2. 系統(tǒng)設(shè)計與調(diào)試

- 設(shè)計大規(guī)模分布式系統(tǒng):需要理解網(wǎng)絡(luò)協(xié)議棧、數(shù)據(jù)一致性、容錯機(jī)制,這些都深深植根于對底層通信和存儲硬件的理解。

- 調(diào)試復(fù)雜問題:當(dāng)遇到難以重現(xiàn)的bug、性能隨機(jī)下降或系統(tǒng)崩潰時,問題根源可能在于硬件層面(如內(nèi)存訪問錯誤、CPU異常)或操作系統(tǒng)與硬件的交互。掌握組成原理知識,能幫助解讀核心轉(zhuǎn)儲(Core Dump)、處理器跟蹤日志等低級調(diào)試信息。

3. 面向未來的設(shè)計

隨著量子計算、神經(jīng)形態(tài)計算等非馮·諾依曼體系結(jié)構(gòu)的發(fā)展,軟件設(shè)計的范式可能發(fā)生根本性變革。具備扎實的計算機(jī)組成與體系結(jié)構(gòu)知識,能使軟件設(shè)計師更好地適應(yīng)和引領(lǐng)這些變化,而非被動跟隨。

###

計算機(jī)組成原理與體系結(jié)構(gòu)并非遠(yuǎn)離日常開發(fā)的“象牙塔”知識。它們是軟件得以運(yùn)行的物理和邏輯基礎(chǔ),是軟件設(shè)計師從“代碼實現(xiàn)者”邁向“系統(tǒng)構(gòu)建者”的必經(jīng)之路。在軟件開發(fā)過程中,有意識地結(jié)合底層思考,不僅能寫出更高效、更健壯的代碼,也能在面對復(fù)雜系統(tǒng)問題時,擁有更深刻的洞察力和更強(qiáng)大的解決能力。將高層抽象設(shè)計與底層運(yùn)行機(jī)制融會貫通,正是杰出軟件設(shè)計師區(qū)別于普通程序員的關(guān)鍵所在。